- 您现在的位置:买卖IC网 > Sheet目录395 > ATMEGA128RFA1-ZUR (Atmel)IC AVR MCU 2.4GHZ XCEIVER 64QFN

�� �

�

�

�ATmega128�

�The� EEPROM� can� not� be� programmed� during� a� CPU� write� to� the� Flash� memory.� The� software�

�must� check� that� the� Flash� programming� is� completed� before� initiating� a� new� EEPROM� write.�

�Step� 2� is� only� relevant� if� the� software� contains� a� boot� loader� allowing� the� CPU� to� program� the�

�Flash.� If� the� Flash� is� never� being� updated� by� the� CPU,� step� 2� can� be� omitted.� See� “Boot� Loader�

�Support� –� Read-� W� hile-� W� rite� Self-Programming� ”� on� page� 273� for� details� about� boot�

�programming.�

�Caution:� An� interrupt� between� step� 5� and� step� 6� will� make� the� write� cycle� fail,� since� the�

�EEPROM� Master� W� rite� Enable� will� time-out.� If� an� interrupt� routine� accessing� the� EEPROM� is�

�interrupting� another� EEPROM� access,� the� EEAR� or� EEDR� Register� will� be� modified,� causing� the�

�interrupted� EEPROM� access� to� fail.� It� is� recommended� to� have� the� global� interrupt� flag� cleared�

�during� the� four� last� steps� to� avoid� these� problems.�

�W� hen� the� write� access� time� has� elapsed,� the� EE� W� E� bit� is� cleared� by� hardware.� The� user� soft-�

�ware� can� poll� this� bit� and� wait� for� a� zero� before� writing� the� next� byte.� W� hen� EE� W� E� has� been� set,�

�the� CPU� is� halted� for� two� cycles� before� the� next� instruction� is� executed.�

�?� Bit� 0� –� EERE:� EEPROM� Read� Enable�

�The� EEPROM� Read� Enable� Signal� EERE� is� the� read� strobe� to� the� EEPROM.� W� hen� the� correct�

�address� is� set� up� in� the� EEAR� Register,� the� EERE� bit� must� be� written� to� a� logic� one� to� trigger� the�

�EEPROM� read.� The� EEPROM� read� access� takes� one� instruction,� and� the� requested� data� is�

�available� immediately.� W� hen� the� EEPROM� is� read,� the� CPU� is� halted� for� four� cycles� before� the�

�next� instruction� is� executed.�

�The� user� should� poll� the� EE� W� E� bit� before� starting� the� read� operation.� If� a� write� operation� is� in�

�progress,� it� is� neither� possible� to� read� the� EEPROM,� nor� to� change� the� EEAR� Register.�

�The� calibrated� Oscillator� is� used� to� time� the� EEPROM� accesses.� Table� 2� lists� the� typical� pro-�

�gramming� time� for� EEPROM� access� from� the� CPU.�

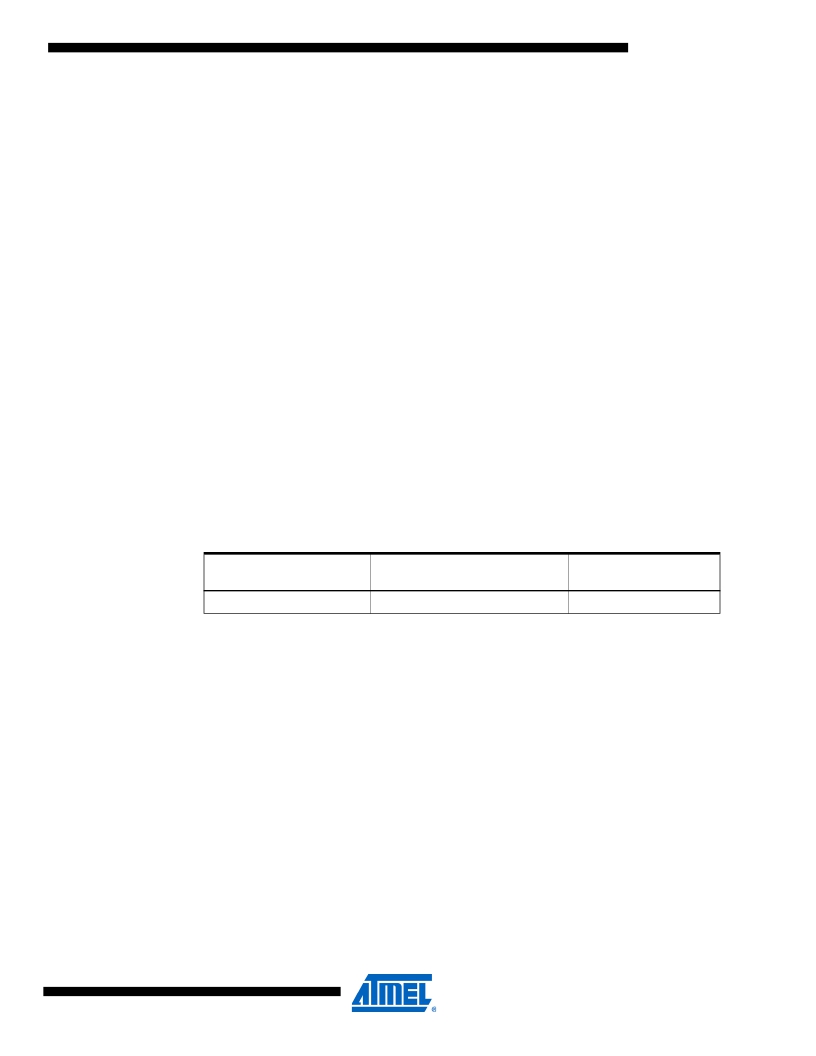

�Table� 2.� EEPROM� Programming� Time�

�Number� of� Calibrated� RC�

�Symbol�

�EEPROM� W� rite� (from� CPU)�

�Oscillator� Cycles� (1)�

�8448�

�Typ� Programming� Time�

�8.5ms�

�Note:�

�1.� Uses� 1MHz� clock,� independent� of� CKSEL-fuse� settings.�

�22�

�2467X–AVR–06/11�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATMEGA64RZAPV-10AU

BUNDLE ATMEGA644P/AT86RF230 TQFP

ATP101-TL-H

MOSFET P-CH 30V 25A ATPAK

ATP102-TL-H

MOSFET P-CH 30V 40A ATPAK

ATP103-TL-H

MOSFET P-CH 30V 55A ATPAK

ATP104-TL-H

MOSFET P-CH 30V 75A ATPAK

ATP106-TL-H

MOSFET P-CH 40V 30A ATPAK

ATP107-TL-H

MOSFET P-CH 40V 50A ATPAK

ATP108-TL-H

MOSFET P-CH 40V 70A ATPAK

相关代理商/技术参数

ATMEGA128RFA1-ZUR SL514

制造商:Atmel Corporation 功能描述:

ATMEGA128RFA1-ZUR00

制造商:Atmel Corporation 功能描述:2.4GHZ 802.15.4 128K SOC REVF 制造商:Atmel Corporation 功能描述:2.4GHZ 802.15.4 128K SOC REVF T&R - Bulk 制造商:Atmel from Components Direct 功能描述:ATMEL ATMEGA128RFA1-ZUR00 MICROCONTROLLERS (MCU) 制造商:Atmel 功能描述:Atmel ATMEGA128RFA1-ZUR00 Microcontrollers (MCU) 制造商:Atmel Corporation 功能描述:MCU AVR 2.4GHZ 128K FLASH 64VQFN 制造商:Atmel Corporation 功能描述:2.4GHZ 802.15.4 128K SOC Revision F 制造商:Atmel 功能描述:2.4GHZ 802.15.4 128K SOC REVF

ATMEGA128RFR2-ZF

功能描述:IC RF TXRX+MCU 802.15.4 64-VFQFN 制造商:microchip technology 系列:- 包装:托盘 零件状态:在售 类型:TxRx + MCU 射频系列/标准:802.15.4 协议:Zigbee? 调制:DSSS, O-QPSK 频率:2.4GHz 数据速率(最大值):2Mbps 功率 - 输出:3.5dBm 灵敏度:-100dBm 存储容量:128kB 闪存,4kB EEPROM,16kB SRAM 串行接口:I2C,JTAG,SPI,USART GPIO:35 电压 - 电源:1.8 V ~ 3.6 V 电流 - 接收:5mA ~ 12.5mA 电流 - 传输:8mA ~ 14.5mA 工作温度:-40°C ~ 125°C 封装/外壳:64-VFQFN 裸露焊盘 标准包装:260

ATMEGA128RFR2-ZU

制造商:Atmel Corporation 功能描述:2.4GHZ 802.15.4 128K SOC IND 85C - Bulk

ATMEGA128RFR2-ZUR

制造商:Atmel Corporation 功能描述:2.4GHZ 802.15.4 128K SOC 85C T&R - Tape and Reel

ATMEGA128RZAV-8AU

功能描述:射频微控制器 - MCU AVR Z-Link Bundle RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:Si100x 数据总线宽度:8 bit 最大时钟频率:24 MHz 程序存储器大小:64 KB 数据 RAM 大小:4 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LGA-42 安装风格:SMD/SMT 封装:Tube

ATMEGA128RZAV-8MU

功能描述:射频微控制器 - MCU AVR Z-Link Bundle RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:Si100x 数据总线宽度:8 bit 最大时钟频率:24 MHz 程序存储器大小:64 KB 数据 RAM 大小:4 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:LGA-42 安装风格:SMD/SMT 封装:Tube